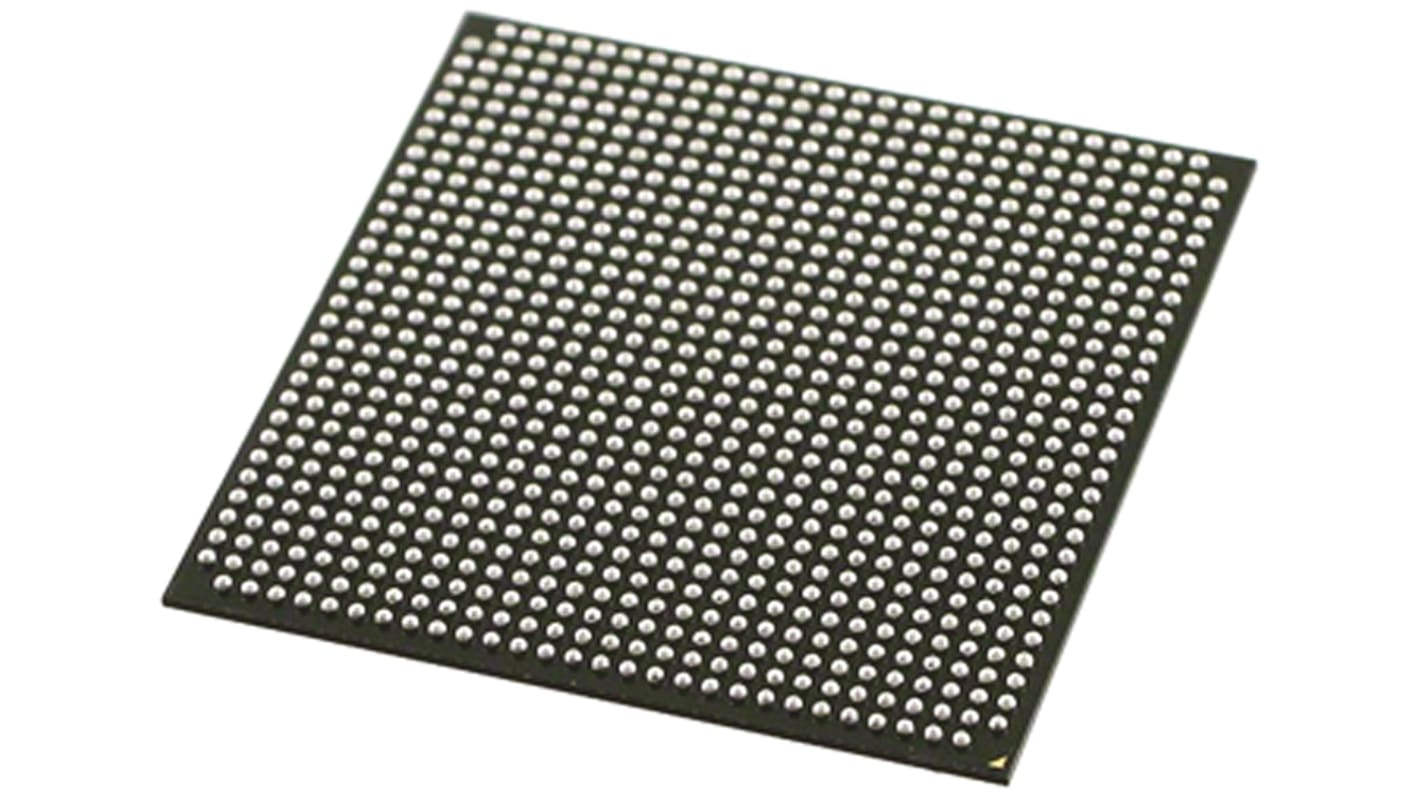

Programovatelné hradlové pole FPGA 5CSXFC5D6F31C8N Cyclone V SX 85000 článků 85000 hradel 4450Ků 32075 bloků 1,07

- Skladové číslo RS:

- 830-3578

- Výrobní číslo:

- 5CSXFC5D6F31C8N

- Výrobce:

- Altera

Využijte množstevní slevu

Mezisoučet (1 jednotka)*

4 532,50 Kč

(bez DPH)

5 484,32 Kč

(s DPH)

Informace o zásobách jsou momentálně nedostupné

Ks | za jednotku |

|---|---|

| 1 - 9 | 4 532,50 Kč |

| 10 - 19 | 4 416,27 Kč |

| 20 + | 4 305,87 Kč |

*orientační cena

- Skladové číslo RS:

- 830-3578

- Výrobní číslo:

- 5CSXFC5D6F31C8N

- Výrobce:

- Altera

Specifikace

Technické reference

Legislativa a životní prostředí

Podrobnosti o výrobku

Výběrem jednoho nebo více atributů si najděte podobné produkty.

Vybrat vše | Atribut | Hodnota |

|---|---|---|

| Značka | Altera | |

| Název řady | Cyclone V SX | |

| Počet logických hradel | 85000 | |

| Počet logických článků | 85000 | |

| Počet logických jednotek | 32075 | |

| Speciální DSP | Ano | |

| Počet registrů | 128300 | |

| Počet násobitelů | 174 (18 x 18) | |

| Typ montáže | Povrchová montáž | |

| Typ balení | FBGA | |

| Počet kolíků | 896 | |

| Počet bitů paměti RAM | 4450K | |

| Délka | 31mm | |

| Maximální provozní napájecí napětí | 1,13 V | |

| Šířka | 31mm | |

| Maximální pracovní teplota | +85 °C | |

| Minimální provozní napájecí napětí | 1,07 V | |

| Minimální provozní teplota | 0 °C | |

| Vybrat vše | ||

|---|---|---|

Značka Altera | ||

Název řady Cyclone V SX | ||

Počet logických hradel 85000 | ||

Počet logických článků 85000 | ||

Počet logických jednotek 32075 | ||

Speciální DSP Ano | ||

Počet registrů 128300 | ||

Počet násobitelů 174 (18 x 18) | ||

Typ montáže Povrchová montáž | ||

Typ balení FBGA | ||

Počet kolíků 896 | ||

Počet bitů paměti RAM 4450K | ||

Délka 31mm | ||

Maximální provozní napájecí napětí 1,13 V | ||

Šířka 31mm | ||

Maximální pracovní teplota +85 °C | ||

Minimální provozní napájecí napětí 1,07 V | ||

Minimální provozní teplota 0 °C | ||

Cyclone FPGA, Altera

FPGA je polovodičové zařízení skládající se z Matrix konfigurovatelných logických bloků (CLB) připojených prostřednictvím programovatelných propojení. Uživatel určuje tato propojení programováním SRAM. CLB může být jednoduché (A, OR Gates, atd.) nebo složité (blok RAM). FPGA umožňuje provedení změn designu i po připájení přístroje do desky s plošnými spoji.

Související odkazy

- FPGA 5CEBA4F17C8N Cyclone V 49000 článků 49000 hradel 3464192ů 18480 bloků 113 V FBGA

- FPGA 5CEBA2F17C8N Cyclone V 25000 článků 25000 hradel 2002944ů 9434 bloků 113 V FBGA

- Programovatelné hradlové pole FPGA 5AGXFB3H4F40C5N Arria V 362000 článků 362k hradel 19358kbitů 362000 bloků 1,07

- Programovatelné hradlové pole FPGA 5AGXFB3H4F35I5N Arria V 362000 článků 362k hradel 19358kbitů 362000 bloků 1,07

- Programovatelné hradlové pole FPGA 5AGXMB1G4F40C4N Arria V 300000 článků 300k hradel 16952kbitů 300000 bloků 1,07

- Programovatelné hradlové pole FPGA EP4CE15F23I8LN Cyclone 15408 článků 15408 hradel 516096ů 963 bloků 0,97 →

- FPGA EP4CE6F17C8N Cyclone 6272 článků 6272 hradel 276480ů 392 bloků FBGA

- FPGA EP4CE6E22I7N Cyclone 6272 článků 6272 hradel 276480ů 392 bloků EQFP