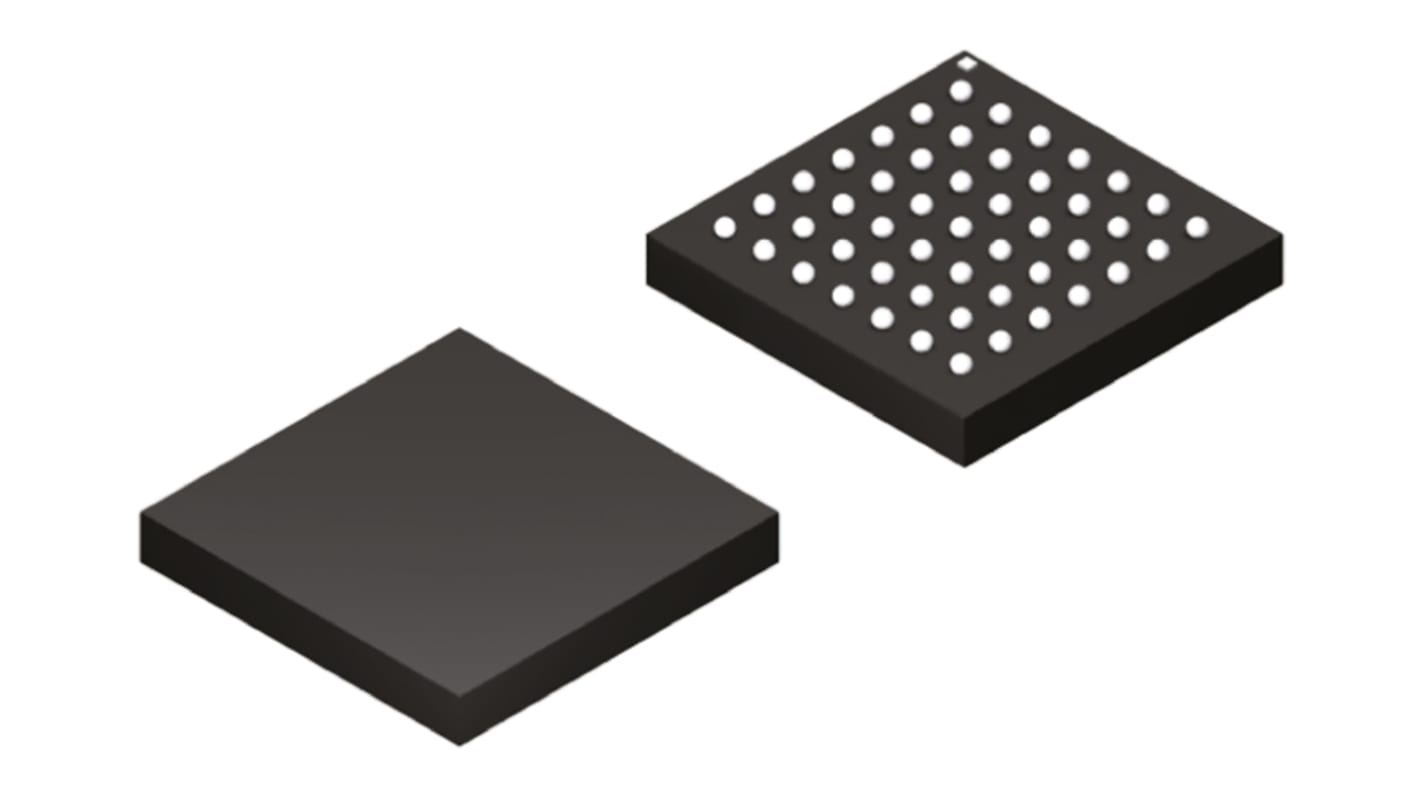

FPGA iCE40LP1K-CM49 iCE40 LP 1280 článků 64kbitů 160 bloků, počet kolíků: 49, UCBGA

- Skladové číslo RS:

- 772-0085P

- Výrobní číslo:

- iCE40LP1K-CM49

- Výrobce:

- Lattice Semiconductor

Mezisoučet 1 jednotka (dodává se na platu)*

94,93 Kč

(bez DPH)

114,87 Kč

(s DPH)

Doprava ZDARMA pro objednávky nad 1 500,00 Kč

Poslední zásoby RS

- Posledních 63 ks/položek skladem k odeslání z jiného místa

Ks | za jednotku |

|---|---|

| 1 + | 94,93 Kč |

*orientační cena

- Skladové číslo RS:

- 772-0085P

- Výrobní číslo:

- iCE40LP1K-CM49

- Výrobce:

- Lattice Semiconductor

Specifikace

Technické reference

Legislativa a životní prostředí

Podrobnosti o výrobku

Výběrem jednoho nebo více atributů si najděte podobné produkty.

Vybrat vše | Atribut | Hodnota |

|---|---|---|

| Značka | Lattice Semiconductor | |

| Název řady | iCE40 LP | |

| Počet logických článků | 1280 | |

| Počet logických jednotek | 160 | |

| Počet registrů | 1280 | |

| Typ montáže | Povrchová montáž | |

| Typ balení | UCBGA | |

| Počet kolíků | 49 | |

| Počet bitů paměti RAM | 64kbit | |

| Rozměry | 3 x 3 x 0.9mm | |

| Výška | 0.9mm | |

| Délka | 3mm | |

| Minimální provozní teplota | -40 °C | |

| Minimální provozní napájecí napětí | 1.14 V | |

| Šířka | 3mm | |

| Maximální provozní napájecí napětí | 1.26 V | |

| Maximální pracovní teplota | +85 °C | |

| Vybrat vše | ||

|---|---|---|

Značka Lattice Semiconductor | ||

Název řady iCE40 LP | ||

Počet logických článků 1280 | ||

Počet logických jednotek 160 | ||

Počet registrů 1280 | ||

Typ montáže Povrchová montáž | ||

Typ balení UCBGA | ||

Počet kolíků 49 | ||

Počet bitů paměti RAM 64kbit | ||

Rozměry 3 x 3 x 0.9mm | ||

Výška 0.9mm | ||

Délka 3mm | ||

Minimální provozní teplota -40 °C | ||

Minimální provozní napájecí napětí 1.14 V | ||

Šířka 3mm | ||

Maximální provozní napájecí napětí 1.26 V | ||

Maximální pracovní teplota +85 °C | ||

Pole programovatelných bran, lattice Semiconductor

FPGA je polovodičové zařízení skládající se z Matrix konfigurovatelných logických bloků (CLB) připojených prostřednictvím programovatelných propojení. Uživatel určuje tato propojení programováním SRAM. CLB může být jednoduché (A, OR Gates, atd.) nebo složité (blok RAM). FPGA umožňuje provedení změn designu i po připájení přístroje do desky s plošnými spoji.