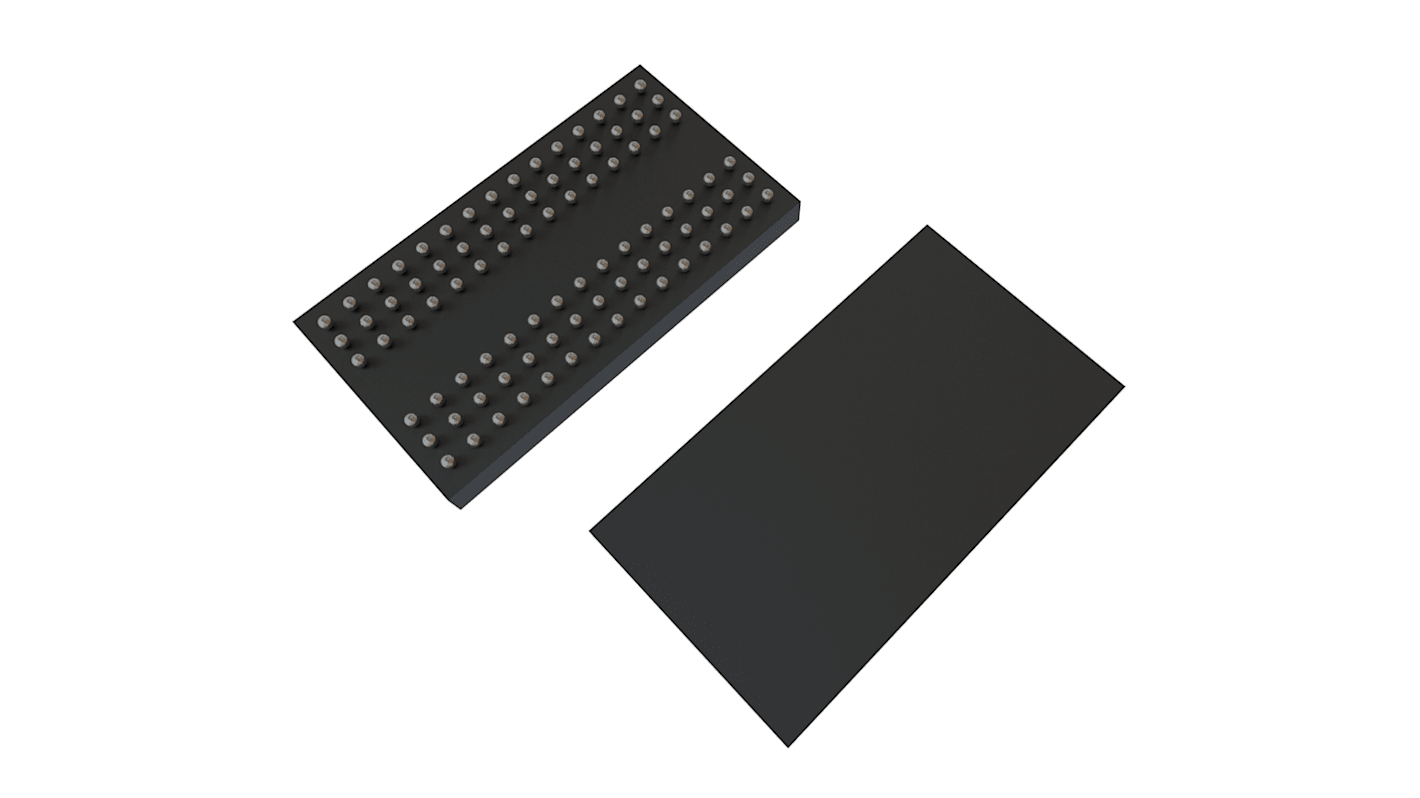

SDRAM W9712G6KB25I, 128Mbit Povrchová montáž 200MHz -40 °C až +95 °C, počet kolíků: 84, 1,7 V až 1,9 V, TFBGA DDR2

- Skladové číslo RS:

- 188-2730

- Výrobní číslo:

- W9712G6KB25I

- Výrobce:

- Winbond

Dočasně není skladem, produkt bude expedován dne 25. 11. 2024. Dodání do 4 pracovních dnů. Doručení může trvat déle z důvodu celního odbavení.

Standardní dodávka

Přidáno

Cena Kus (v jednotce baleni à 5)

50,26 Kč

(bez DPH)

60,81 Kč

(s DPH)

| Ks | Per unit | za balení* |

| 5 - 5 | 50,26 Kč | 251,28 Kč |

| 10 - 15 | 45,70 Kč | 228,48 Kč |

| 20 - 45 | 44,88 Kč | 224,40 Kč |

| 50 - 95 | 44,30 Kč | 221,52 Kč |

| 100 + | 39,79 Kč | 198,96 Kč |

| *orientační cena | ||

- Skladové číslo RS:

- 188-2730

- Výrobní číslo:

- W9712G6KB25I

- Výrobce:

- Winbond

Technické reference

Legislativa a životní prostředí

Podrobnosti o výrobku

W9712G6KB je 128M bitů DDR2 SDRAM a rychlost zahrnuje -25, 25I a -3.

Architektura Double Data Rate: dva datové přenosy během jednoho taktu

Čekací doba CAS: 3, 4, 5 a 6

Délka impulzu: 4 a 8

Obousměrné diferenciální datové pulzy (DQS a /DQS ) jsou vysílány/přijímány spolu s daty

Zarovnání ke kraji při čtení dat a zarovnání na střed při zápisu dat

DLL zarovnává DQ a DQS na hodiny

Diferenciální vstupy hodin (CLK a /CLK)

Datové masky (DM) pro zápis dat

Příkazy zadávané na každém kladném okraji CLK, datové a datové masce odkazují na oba okraje /DQS

Posted/CAS programovatelná latence aditiv podporována pro zajištění účinnosti příkazů a datových sběrnic

Přečtená čekací doba = Additional latence plus CAS latence (RL = AL + CL)

Nastavení impedance Off-Chip-Driver (OCD) a On-Die-Termination (ODT) pro vyšší kvalitu signálu

Operace automatického nabíjení pro impulzy při čtení a zápisu

Režimy automatického obnovení a samo-obnovení

Vypnutí před nabitím a aktivní vypnutí

Zapsat masku dat

Čekací doba zápisu = čekací doba čtení - 1 (WL = RL - 1)

Rozhraní: SSTL_18

Čekací doba CAS: 3, 4, 5 a 6

Délka impulzu: 4 a 8

Obousměrné diferenciální datové pulzy (DQS a /DQS ) jsou vysílány/přijímány spolu s daty

Zarovnání ke kraji při čtení dat a zarovnání na střed při zápisu dat

DLL zarovnává DQ a DQS na hodiny

Diferenciální vstupy hodin (CLK a /CLK)

Datové masky (DM) pro zápis dat

Příkazy zadávané na každém kladném okraji CLK, datové a datové masce odkazují na oba okraje /DQS

Posted/CAS programovatelná latence aditiv podporována pro zajištění účinnosti příkazů a datových sběrnic

Přečtená čekací doba = Additional latence plus CAS latence (RL = AL + CL)

Nastavení impedance Off-Chip-Driver (OCD) a On-Die-Termination (ODT) pro vyšší kvalitu signálu

Operace automatického nabíjení pro impulzy při čtení a zápisu

Režimy automatického obnovení a samo-obnovení

Vypnutí před nabitím a aktivní vypnutí

Zapsat masku dat

Čekací doba zápisu = čekací doba čtení - 1 (WL = RL - 1)

Rozhraní: SSTL_18

Specifikace

Vlastnost | Hodnota |

|---|---|

| Velikost paměti | 128Mbit |

| Třída SDRAM | DDR2 |

| Organizace | 16M x 8 bitů |

| Přenosová rychlost | 200MHz |

| Šířka datové sběrnice | 16bit |

| Šířka adresové sběrnice | 15bit |

| Počet bitů na slovo | 8bit |

| Maximální čas náhodného přístupu | 0.4ns |

| Počet slov | 16M |

| Typ montáže | Povrchová montáž |

| Typ balení | TFBGA |

| Počet kolíků | 84 |

| Rozměry | 12.6 x 8.1 x 0.8mm |

| Výška | 0.8mm |

| Délka | 12.6mm |

| Minimální provozní teplota | -40 °C |

| Šířka | 8.1mm |

| Maximální pracovní teplota | +95 °C |

| Minimální provozní napájecí napětí | 1,7 V |

| Maximální provozní napájecí napětí | 1,9 V |